Lielākais čipa izmēra rekords skan šaubīgi, bet ne tad, ja runa ir par TSMC. Uzņēmums piedāvāja čipu iepakojuma tehnoloģiju uz plāksnes uz pamatnes (CoWoS), kas ļaus izveidot paketes-sistēmas (SiP), kas ir daudzkārt lielākas nekā esošie NVIDIA B200 vai AMD Instinct MI300X procesori. Procesori būs monstruāli lieli ar izmēru 120 x 120 mm un patērēs kilovatus enerģijas.

«CoWoS®, SoIC un System-on-Wafer (TSMC-SoW™): TSMC mikroshēma uz plāksnes uz pamatnes (CoWoS) ir kļuvusi par mākslīgā intelekta revolūcijas galveno faktoru, ļaujot klientiem izmantot vairāk procesoru kodolu un augstas jaudas atmiņu (HBM), kas tiek novietota blakus viena otrai uz vienas starpposmes ierīces. Šajā pašā laikā mūsu integrēto mikroshēmu sistēma (SoIC) ir izrādījusies par vadošo risinājumu 3D čipu velknēšanā un klienti arvien biežāk apvieno CoWoS ar SoIC un citiem komponentiem, lai panāktu maksimālu sistēmas integrāciju pakuē (SiP)».

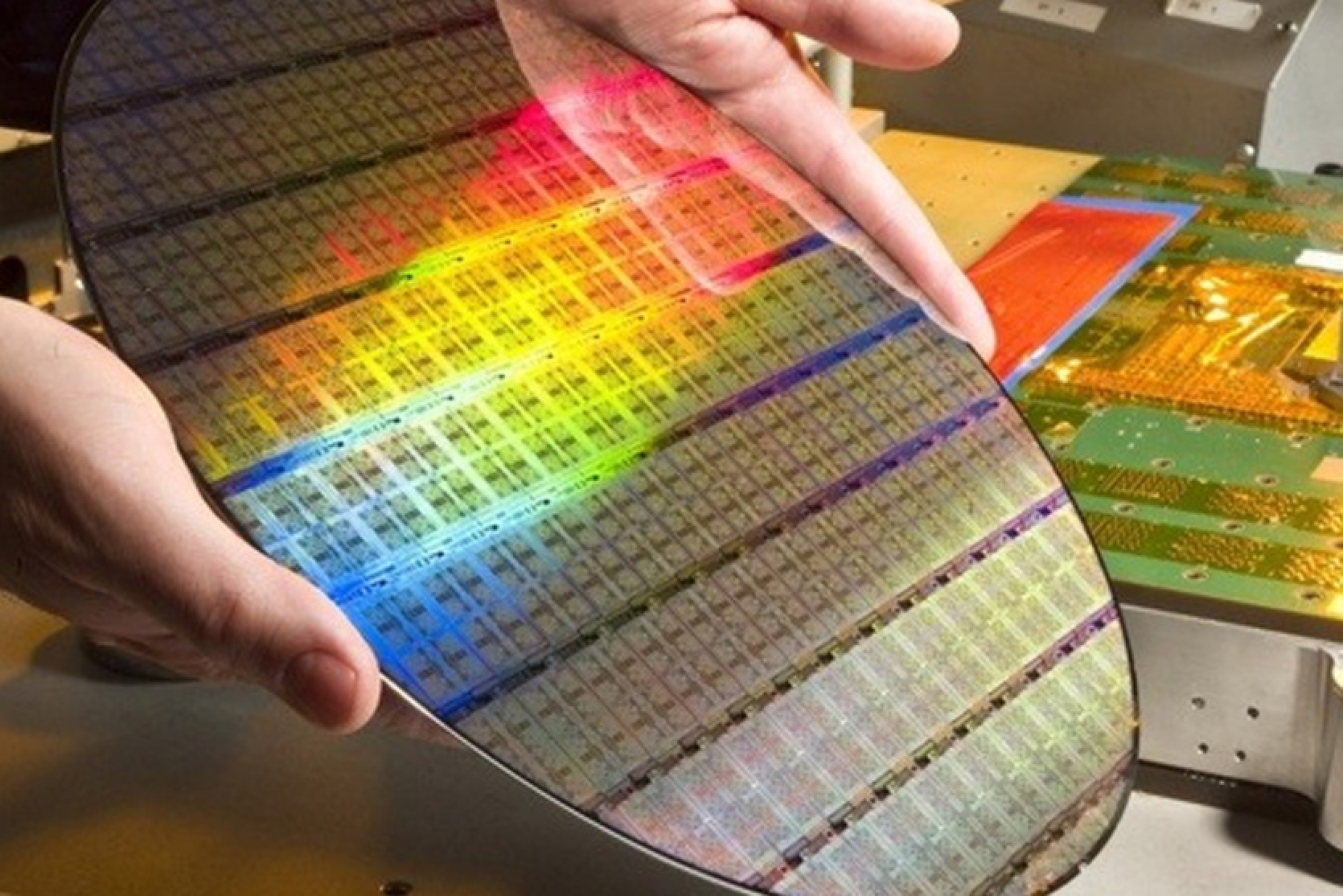

Pateicoties System-on-Wafer, uzņēmums TSMC piedāvā jaunu revolucionāru iespēju, kas ļauj izmantot lielu skaitu matricu uz 300 mm plāksnes, nodrošinot lielāku skaitļošanas jaudu, aizņemot daudz mazāk vietas datu apstrādes centrā un palielinot veiktspēju uz vatu kārtām. Pirmā TSMC SoW piedāvājums, loģiskās shēmas plāksne, balstīta uz Integrated Fan-Out (InFO) tehnoloģiju, jau ir ražošanā. 2027. gadā ir plānota chip-on-wafer versija, kas izmanto CoWoS tehnoloģiju, kas ļaus integrēt SoIC, HBM un citas sastāvdaļas, lai izveidotu spēcīgu plāksnes līmeņa sistēmu ar skaitļošanas jaudu, kas būs salīdzināma ar datu apstrādes centra servera režģa sistēmu vai pat ar veselu serveri».

Platforma izmanto agrāk izstrādāto InFO_SoW tehnoloģiju, kas ļauj veidot lielas čipu izmērus, kā arī System on Integrated Chips (SoIC) tehnoloģiju. Cits tehnoloģijas, Chip-on-Wafer (CoW), ļauj novietot virsma atmiņu vai citas sastāvdaļas.

Būtībā runa ir par procesoriem, kuri ir salīdzināmi ar veselu 300 mm silīcija plāksni izmēros un ļaus novietot milzīgu kodolu skaitu. Šādas kodolu pakošanas metodes nodrošinās veiktspējas un energoefektivitātes palielināšanos, izmantojot augstas ātrdarbības starpkomponentu savienojumus. Sistēmā būs zemas kavēšanās starp kodoliem un zems pretestības līmenis enerģijas pārraides laikā. Atšķirībā no iepriekšējām tehnoloģijām, CoWoS ļauj izmantot dažādas tehnoloģiskās proceses un ātrdarbības atmiņu HBM4 čipu kompozīcijā.

Avoti: TSMC, Tom`s Hardware

Komentāri (0)

Šobrīd nav neviena komentāra